고정 헤더 영역

상세 컨텐츠

본문

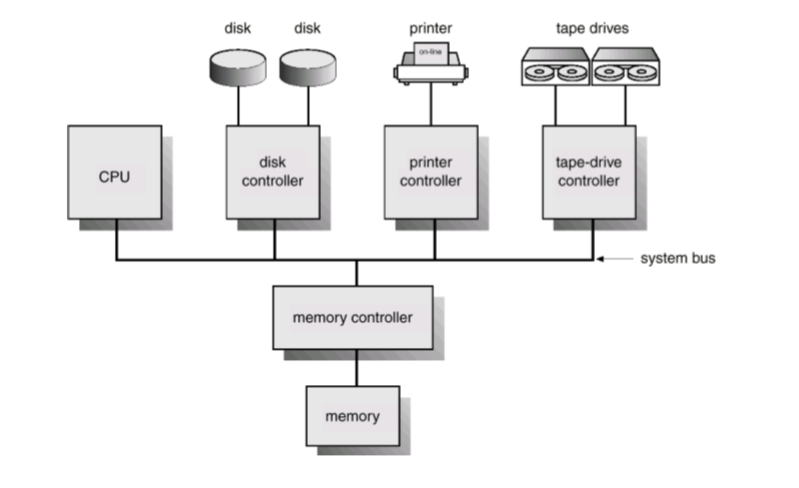

현대 컴퓨터 시스템 구조

○ 하나 이상의 CPU와 device controller가 common bus를 통해 연결됨

○ Common bus 는 공유 메모리 접근을 제공함

Device Controller

○ 대개 특정 유형의 device 동작을 책임짐 - 오디오, 비디오, 디스크

○ USB 제어기 (Universal serial bus) - 다양한 device와 연결 가능

1.2.1 컴퓨터 시스템 동작

Bootstrap Program :

○ 컴퓨터 전원을 켰을 때 혹은 reboot될 때에 수행되는 initial program (초기 프로그램)

○ 대개 비휘발성 메모리인 firmwre (ROM, EPROM)에 저장됨

Bootstrap program의 동작 :

1. 시스템의 모든 부분을 초기화 (CPU 레지스터, device controller, 메모리 내용 등)

2. 운영체제 적재 및 실행 : 커널이 지정된 위치를 알고 있어서 메모리에 적재하고, 적재된 운영체제를 실행시킴

System Service Program

System service (system daemon) :

일부 서비스들은 커널이 수행되는 동안 항상 수행되지만, 커널에 포함되지 않고 외부 프로그램으로 제공됨

커널 수행 후 동작 :

1. 커널 부팅 후에 최초의 system service 수행 (UNIX에서는 "init")

2. 이어서 많은 다른 daemon들의 실행을 시작

3. Event 발생을 기다림 -> event가 발생하면 OS가 처리를 수행

EVENT = Interrupt

***Interrupt

하드웨어 또는 소프트웨어에 의해서 발생되어 CPU에 보내지는 신호

즉각적인 처리를 필요로 하는 event가 발생되었음을 알림

Interrupt 유형

Hardware interrupt : 외부 입출력 장치에 의해 발생 (anytime에 발생 가능)

Software interrupt : OS 서비스를 요청하기 위해 SW에 의해서 발생 (특별한 instruction 사용)

Internal interrupt : SW실행 오류를 처리하기 위해 CPU 내부에서 발생 (divide by zero, invaild memory access)

interrupt 용어

Hardware interrupt : interrupt (좁은 의미)

Software interrupt : System call

Internal interrupt : Trap, Exception (좁은 의미)

넓은 의미로는 interrupt = trap, exception (모든 종류의 interrupt)

운영체제와 interrupt의 관계

운영체제 동작은 "interrupt driven"이다

운영체제는 적절한 인터럽트 처리 동작을 수행함

"No interrupt, No work" 인터럽트가 없으면 일을 안한다.

Interrupt에 대한 운영체제의 역할

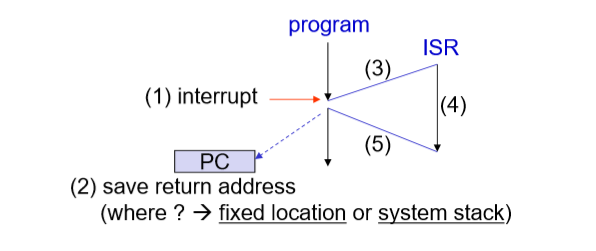

Interrupt Sequence

CPU가 인터럽트 신호를 받으면

1. 현재 수행중인 작업을 멈춤

2. 인터럽트된 instruction의 주소를 저장 (특정 위치 or system stack)

3. interrupt service routine(ISR)의 주소를 찾음

4. ISR 실행 시작

ISR실행이 완료되면

5. 저장된 return 주소로 되돌아 가서 인터럽트된 instruction 실행을 재개함

Interrupt Service Routine 주소 결정

(주소 결정 단계는 하드웨어에서 이루워짐)

Polled Interrupt :

1. 인터럽트 정보를 조사하기 위해 특정 위치에 있는 general polling routine을 호출

2. 이 루틴에서 장치를 polling하여 인터럽트 정보를 찾아서 interrupt-specific처리 루틴을 호출

Polling : 장치가 10개가 있으면 10개에 일일이 조사해서 어느장치에서 요청햇는지 알리는 것

단점 : 시간이 많이걸림

Vectored Interrupt :

1. 인터럽트 요청과 함께 unique number가 제공됨

2. Interrupt vector table에 ISR의 주소들이 저장되며 unique number는 이 table의 index로 사용되어 ISR의 주소를 읽어서 해당 주소의 루틴을 호출

장점 : Polling 과정이 없어 빠른 interrupt 처리가 가능

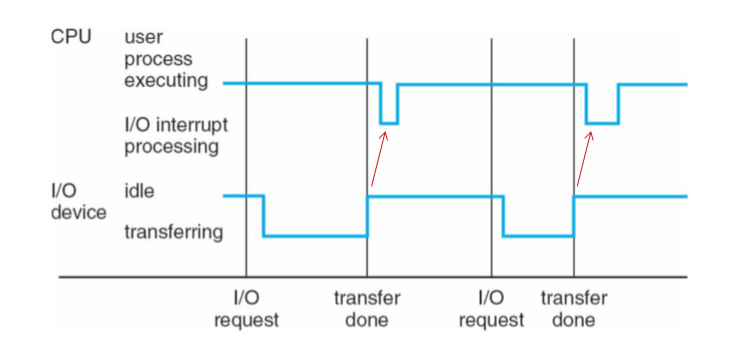

Interrupt Time Line

I/O device와 CPU는 동시에 실행 가능

I/O device가 입출력 전송을 완료할 때에 대개 CPU에 인터럽트

cpu하고 i/o장치는 동시에 수행을 할 수 있음

cpu가 i/o에 전송을하고 그동안 cpu는 다른 일을 하고있음

i/o장치가 다 받고 이거 사용해도 된다 라고 cpu에게 인터럽트 요청함

cpu는 하던일을 멈추고 요청한 인터럽트를 수행함

사용자가 입력받고싶다 그럼 systemcall -> os에서 입출력을 할수 있는 i/o장치에 인터럽트를 보냄

특정 프로그램이 cpu를 너무 오래쓰면 timer interrupt를 발생시킴. 그러면 프로그램이 바뀔 수 있음

1.2.2 Storage 구조

주기억장치(Main Memory)

CPU는 주기억장치 만 memory address를 사용하여 직접 접근 가능 -> 실행할 프로그램이 주기억장치에 적재되어야 함

주기억장치로 대개 DRAM(dynamic RAM)을 사용함

Von Neumann 구조

프로그램(명령어)과 데이터가 주기억장치에 함께 저장됨

실행 과정

1. 명령어를 주기억장치에서 fetch하여 instruction register에 저장

2. 연산에 필요한 데이터(operand)를 주기억장치에서 읽음

3. 명령어의 연산 실행

4. 결과 데이터를 주기억장치에 저장

주기억장치의 한계

모든 프로그램과 데이터를 주기억장치에 영구히 저장할 수 없음

이유) 1. 기억 용량 제한, 2.휘발성 (전원이 공급되는 동안만 기억)

보조 저장장치

기억용량이 큰 비휘발성 메모리 제공 (대개 HDD가 사용됨)

다양한 저장장치의 계층 구조

electronic disk 는 휘발성, 비휘발성 모두 가능. (eletornic disk 기점으로 위로는 휘발성, 밑으로는 비휘발성)

캐싱 (caching) :

정보를 일시적으로 더 빠른 저장장치로 복사하는 것

EX) 캐시메모리 - 주기억장치 내용을 복사하는 빠른 메모리 (SW에게 보이지 않음) MEMORY -> CACHE (HW관리)

주기억장치는 보조저장장치의 캐시로 사용될 수 있음 (OS 관리)

1.2.3 I/O 구조

I/O device와 CPU간의 데이터 전송은 device controller를 통하여 수행됨

Device Controller

○ 각 device controller는 특정 유형의 device 동작 제어를 담당함

○ 여러 개의 device를 부착가능한 device controller도 존재함 (EX) SCSI(Small Computer Systems Interface) controller

○ device controller는 local buffer와 특수용도의 register들을 갖고 있음

○ 주변장치(I/O device)와 local buffer간의 데이터 전송을 담당

Device Driver

*** I/O data transfer

Main memory <-> Local buffer (by CPU)

Local buffer <-> the device (by device controller)

많은 부분의 OS코드는 I/O 동작 관리에 할애됨

이유 ) I/O동작관리가 시스템의 신뢰성과 성능에 중요하고 장치의 특성이 종류에 따라서 다양하기 때문

Device driver

OS는 device 별로 Device driver 프로그램을 갖고 있음

동작 : Device controller의 동작을 이해하여 I/O 동작을 제어하고, OS의 다른 부분에게 device에 대한 uniform interface 제공

I/O 동작

I/O 동작 과정

1. Device driver가 device controller의 적절한 register에 필요한 값을 적재

2. Device controller가 register 내용을 조사하여 수행할 동작을 결정

3. Device controller는 수행할 동작에 따라서 I/O 전송을 시작함

4. I/O전송 완료 후 Device controller는 interrupt를 통해 Device driver에게 완료를 알림

5. Device driver는 제어를 운영체제에게 반환 (결과도 같이 반환)

I/O 동작 유형

1. Programmed I/O (Polling)

2. Interrupt-driven I/O

3. Direct memory access(DMA) based I/O

Programmed I/O (Polling)

Polling :

CPU가 프로그램이 상태정보를 반복하여 조사하면서 I/O 전송 완료를 대기함 (status register가 사용됨)

I/O 전송이 완료되면 CPU는 device controller와 memory간의 데이터 전송을 수행함

(즉, 부하(device controller)한테 일을 시키고 상사(CPU)가 계속 부하를 지켜보는 것)

단점 : I/O 동작이 진행되는 동안 CPU는 다른 작업을 수행할 수 없음

-> 해결 : interrupt-driven I/O

Interrupt-driven I/O

I/O전송 완료를 interrupt를 통하여 CPU에게 알림

CPU는 I/O전송을 시작한 후에 다른 작업 수행 가능

(즉, 부하한테 일을 시키고 CPU는 부하가 완료했다고 하기 전까지 다른 일을 함)

I/O 전송 완료 후

device controller는 interrupt를 경유하여 device driver에게 알림

CPU는 device driver의 interrupt handler 프로그램을 수행하여 device controller와 memory간에 데이터를 전송함

단점 : 적은 양의 데이터 전송에는 문제가 없느나 DISK I/O와 같은 대량의 데이터 전송에 빈번한 interrupt로 인해 overhead가 큼

-> 해결 : DMA(direct memory access)

Direct Memory Access(DMA)

CPU 개입없이 device controller의 제어에 의해 device controller의 local buffer와 memory간에 직접 데이터 전송을 수행

메모리 속도에 근접한 속도로 전송 가능 -> 고속 I/O device 전송에 사용

CPU는 DMA I/O동작의 초기화 작업은 수행하지만 데이터 전송에 참여하지는 않음

DMA operation

1. CPU는 data전송 유형과 DMA에 필요한 메모리 pointer, counter(전송량), buffer를 설정함 (초기화 작업)

2. DMA controller는 DMA 방식으로 데이터 전송을 수행

3. 데이터블록 전송이 완료될 때에 DMA controller는 CPU에 interrupt 신호

Interrupt driven I/O와 DMA 방식의 비교

DMA : 블록 전송 당 1회의 interrupt

Interrupt-driven I/O : byte(word) 전송 당 1회의 interrupt

'Computer Science > OS Concepts' 카테고리의 다른 글

| 1.6 ~ 1.9 자원 관리 (Process, Memory, Storage) (0) | 2020.04.04 |

|---|---|

| 1.5 운영체제 연산 (0) | 2020.04.04 |

| 1.4 운영체제의 구조 (0) | 2020.04.04 |

| 1.3 컴퓨터 시스템 구조 (0) | 2020.04.04 |

| 1.1 운영체제가 하는 일 (0) | 2020.04.04 |

댓글 영역