고정 헤더 영역

상세 컨텐츠

본문

3.5 정수의 산술 연산

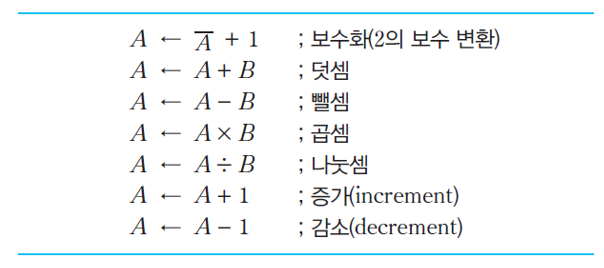

기본적인 산술 연산들

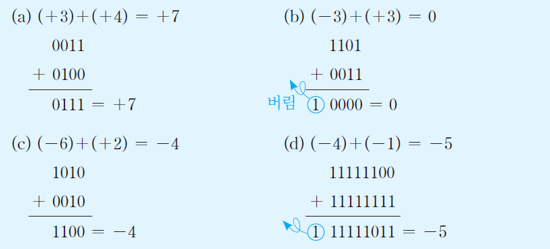

3.5.1 덧셈

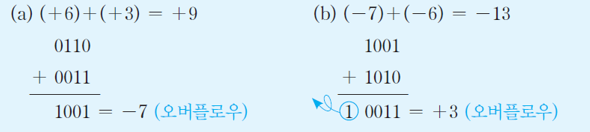

2의 보수로 표현된 수들의 덧셈 방법 : 두 수를 더하고, 만약 올림수가 발생하면 버림

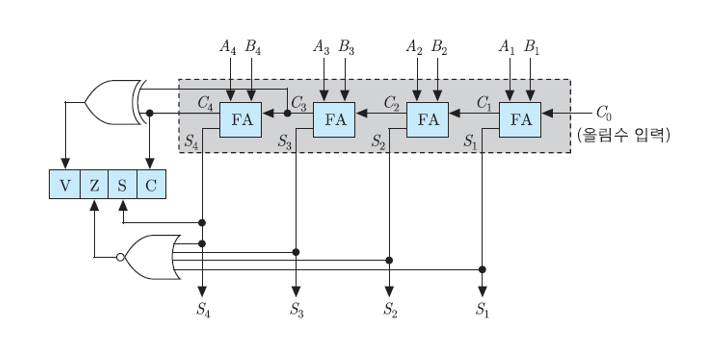

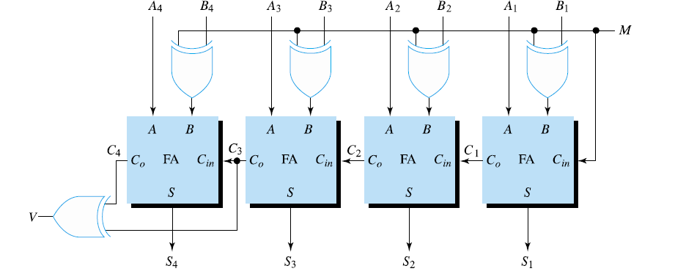

병렬 가산기 (parallel adder)

- 덧셈을 수행하는 하드웨어 모듈

- 비트 수만큼의 전가산기(full-adder)들로 구성

- 덧셈 연산 결과에 따라 해당 조건 플래그들(condition flags)을 세트

> C Flag : 올림수(Carry)

> S Flag : 부호 (Sign)

> Z Flag : 0 (Zero)

> V Flag : 오버플로우(Overflow)

4-비트 병렬 가산기와 상태 비트 제어회로

덧셈 오버플로우 : 덧셈 결과가 그 범위를 초과하여 결과값이 틀리게 되는 상태

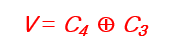

검출 방법 : 두 올림수(carry)들 간의 exclusive-OR를 이용 -> V Flag가 1이면 Overflow.

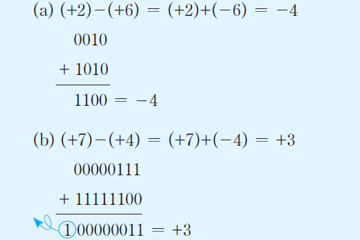

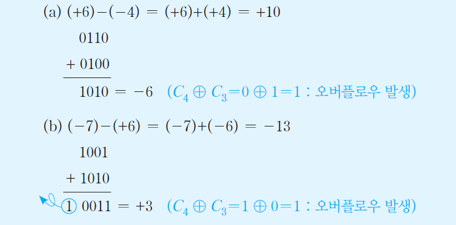

3.5.2 뺄셈

덧셈을 이용하여 수행 (A : 피감수 (minuend), B : 감수(subtrahend))

A - (+B) = A + (-B)

A - (-B) = A + (+B)

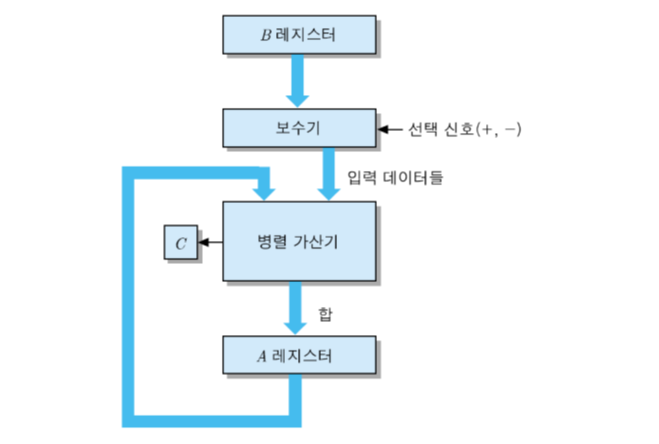

덧셈과 뺄셈 겸용 하드웨어의 블록 구성도

4-비트 병렬 가감산기

- 4-비트 데이터들 간의 덧셈(A+B) 및 뺄셈(A-B)을 모두 수행하는 조합회로

- 제어신호 M=0 : 덧셈, M=1 : 뺄셈(입력 B의 비트들을 반전하고, 최하위 올림수로서 M을 입력)

뺄셈 오버플로우 : 뺄셈 결과가 그 범위를 초과하여 결과값이 틀리게 되는 상태

검출 방법 : 덧셈과 동일

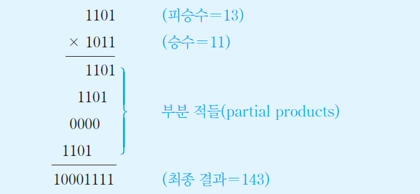

3.5.3 부호 없는 정수의 곱셈

방법 : 각 비트에 대하여 부분 적(partial product) 계산 -> 부분 적들을 모두 더하여 최공 결과를 얻음

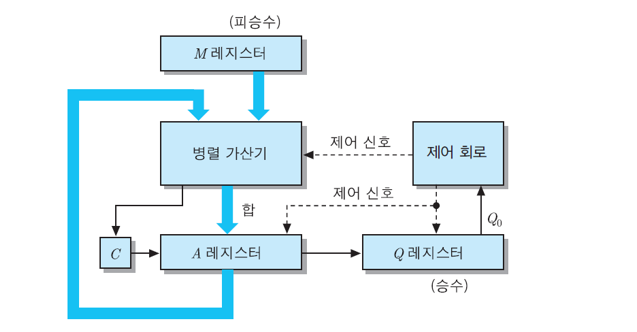

부호 없는 정수 승산기의 하드웨어 구성도

- M 레지스터 : 피승수 (multiplicand) 저장

- Q 레지스터 : 승수 (multiplier) 저장

- 두 배 길이의 결과값은 A 레지스터와 Q 레지스터에 저장

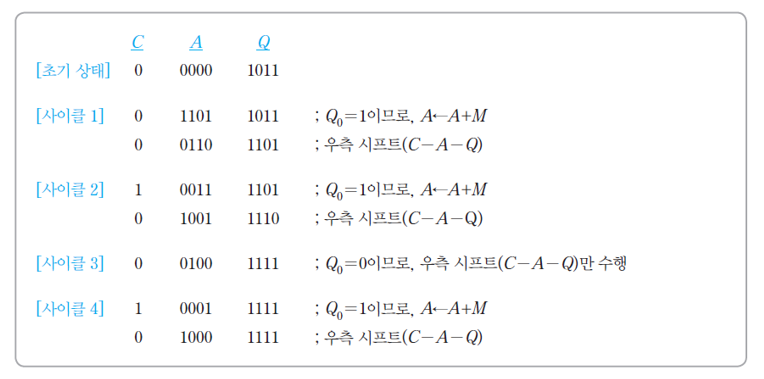

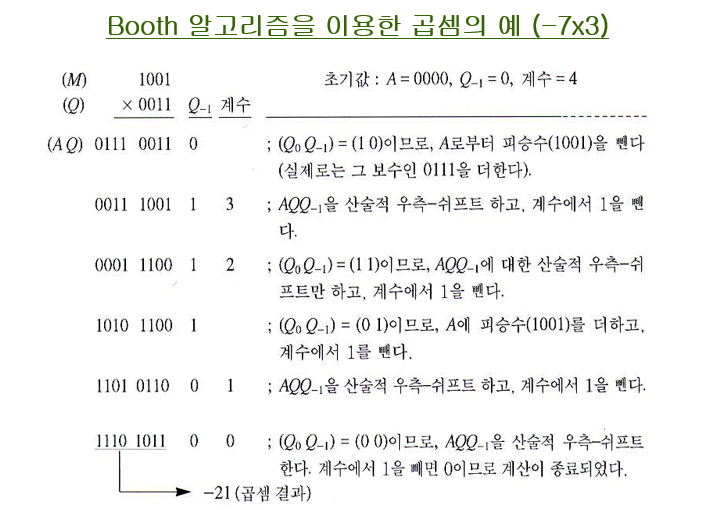

2의 보수들 간의 곱셈

- Booth 알고리즘 (Booth's algorithm) 사용

- 하드웨어 구성

> 부호 없는 정수 승산기의 하드웨어에 다음 부분을 추가

1. M 레지스터와 병렬 가산기 사이에 보수기(complementer) 추가

2. Q 레지스터의 우측에 Q-1이라고 부르는 1-비트 레지스터를 추가하고, 출력을 Q0와 함께 제어 회로로 입력

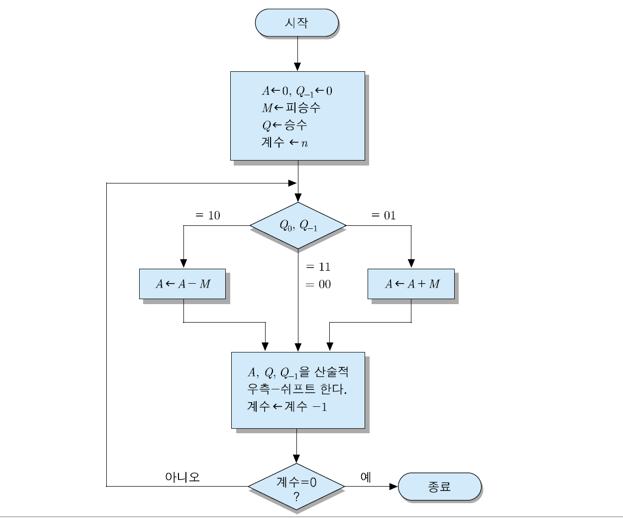

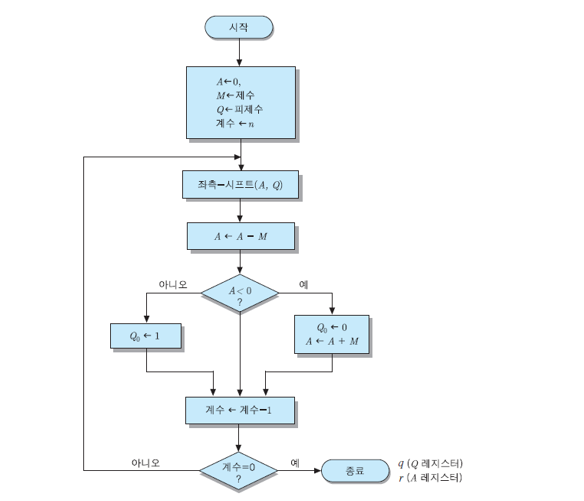

Booth 알고리즘의 흐름도

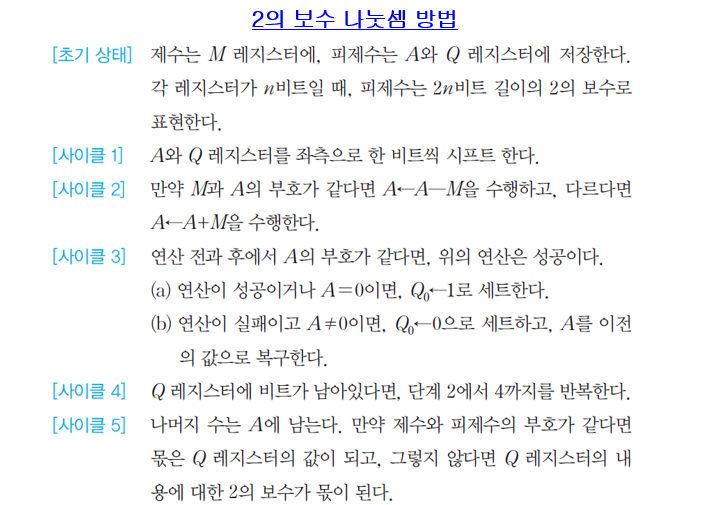

3.5.4 나눗셈

나눗셈의 수식 표현 :

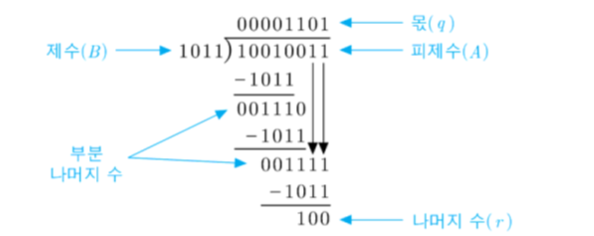

부호 없는 2진 나눗셈 :

부호 없는 2진 나눗셈 알고리즘의 흐름도

'Computer Science > Computer Architecture' 카테고리의 다른 글

| 04. 제어 유니트 (1) [제어 유니트의 기능/구조] (0) | 2020.04.22 |

|---|---|

| 03. 컴퓨터 산술과 논리 연산 (4) [부동소수점 수의 표현/연산] (0) | 2020.04.17 |

| 03. 컴퓨터 산술과 논리 연산(2) [논리 연산, 시프트 연산] (0) | 2020.04.08 |

| 03. 컴퓨터 산술과 논리 연산 (1) [ALU의 구성 요소, 정수의 표현] (0) | 2020.04.08 |

| 02. CPU의 구조와 기능 (3) [명령어 세트] (0) | 2020.04.03 |

댓글 영역