고정 헤더 영역

상세 컨텐츠

본문

5.3.1 RAM (Random Access Memory)

특성

- 임의 엑세스 방식 사용

- 반도체 집적회로 기억장치 (semiconductor IC memory)

- 데이터 읽기와 쓰기가 모두 가능

- 휘발성 (volatile) : 전원 공급이 중단되면 내용이 지워짐

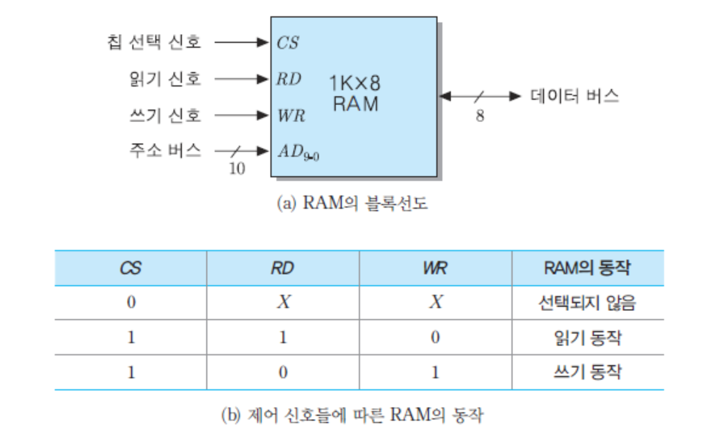

1K x 8 RAM 칩과 제어 신호들

1K = RAM 안에 있는 기억장소의 개수, 8 = 기억장소안에 있는 비트 수

- 주소비트 : 기억장소의 개수가 1K = 2^10이므로 주소 비트는 10비트

- 데이터 버스 폭 : 데이터 입출력은 한 번에 8비트씩 이루어지기 때문에, 데이터 버스의 폭은 8비트

제조 기술에 따른 분류

DRAM (Dynamic RAM)

- 캐패시터(capacitor)에 전하(charge)를 충전하는 방식으로 데이터를 저장하는 기억 소자들(memory cells)로 구성

> 집적 밀도가 높다.

- 데이터의 저장 상태를 유지하기 위하여 주기적인 재충전(refresh) 필요

- 집적 밀도가 더 높으며, 같은 용량의 SRAM 보다 비트당 가격이 더 저렴

- 용량이 큰 주기억장치로 사용

SRAM (Static RAM)

- 기억 소자로서 플립-플롭(flip-flop)을 이용

> 집적 밀도가 낮다

- 전력이 공급되는 동안에는 재충전 없이도 데이터 계속 유지 가능

- DRAM보다 다소 더 빠르다

- 높은 속도가 필요한 캐시 메모리로 사용

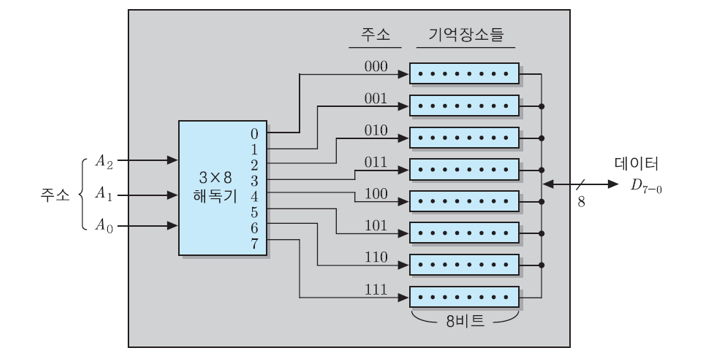

[EXAMPLE] 64-bit RAM의 내부 조직 : 8 X 8 비트 조직

- 8비트로 이루어진 8개의 기억 장소들로 구성

- 주소 비트 수 = 3, 데이터 입출력 선의 수 = 8

용량에 따른 주소 비트 수

1. 8Kbit RAM : 1K x 8비트 조직인 경우, 주소 = 10비트 필요

2. 1Mbit RAM : 128K x 8비트 조직인 경우, 주소 = 17비트 필요

3. 1Gbit RAM : 128M x 8비트 조직인 경우, 주소 = 27비트 필요

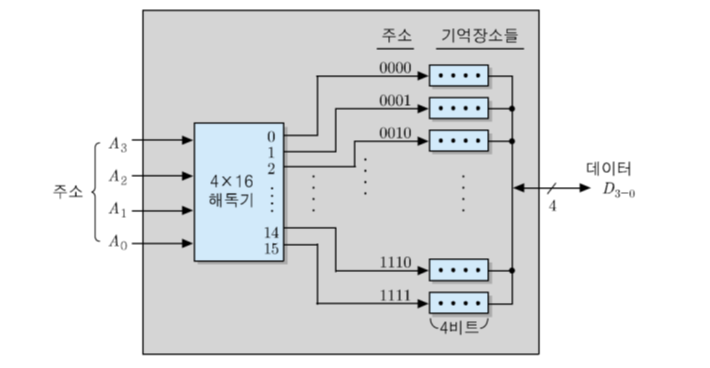

[EXAMPLE] 64-bit RAM의 내부 조직 : 16 X 4 비트 조직

- 4비트로 이루어진 16개의 기억장소 들로 구성

- 주소 비트 수 = 4, 데이터 입출력 선의 수 = 4

용량에 따른 주소 비트 수

1. 8Kbit RAM : 2K x 4비트 조직인 경우, 주소 = 11비트 필요

2. 1Mbit RAM : 256K x 4비트 조직인 경우, 주소 = 18비트 필요

3. 1Gbit RAM : 256M x 4비트 조직인 경우, 주소 = 28비트 필요

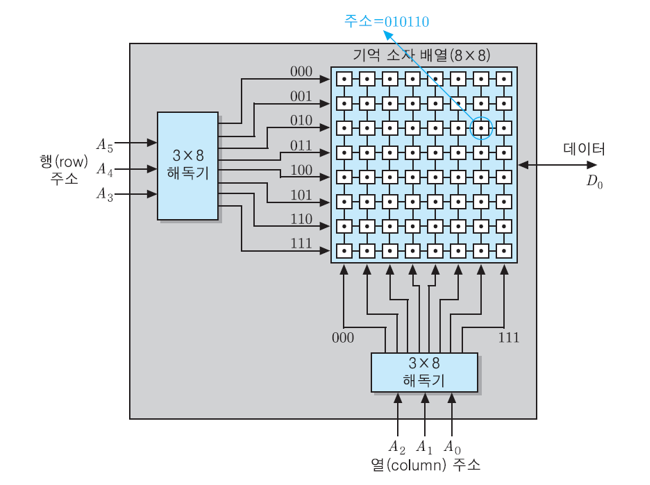

[EXAMPLE] 64-bit RAM의 내부 조직 : 64 X 1 비트 조직

- 한 비트 씩 저장하는 64개의 기억 장소들로 구성

- 6개의 주소 비트들이 필요 (2^6 = 64)

> 상위 3비트들은 8개의 행(row)들 중에서 한 개를 선택하고

> 하위 3비트들은 8개의 열(column)들 중에서 한 개를 선택

- 두 개의 3x8 해독기 필요

- 데이터 입출력 선의 수 = 1

용량에 따른 주소 비트 수

1. 8Kbit RAM : 8K x 1비트 조직인 경우, 주소 = 13비트 필요

2. 1Mbit RAM : 1M x 1비트 조직인 경우, 주소 = 20비트 필요

3. 1Gbit RAM : 1G x 1비트 조직인 경우, 주소 = 30비트 필요

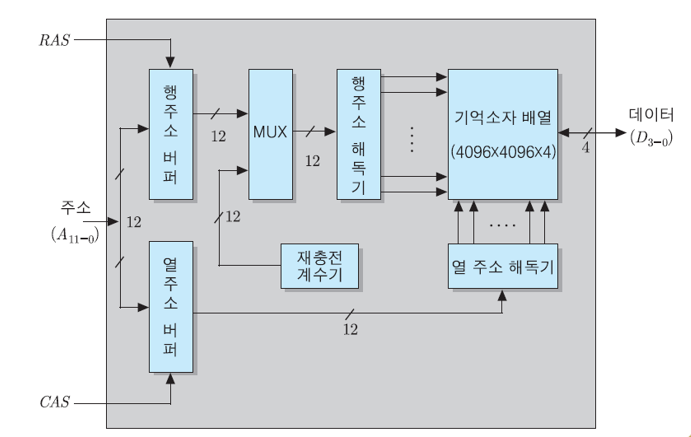

[EXAMPLE] RAM의 내부 조직 : 16M X 4 비트 조직 (64Mbit)

기억 소자들이 4096 x 4096 x 4비트 형태로 배열

- 4096개의 열과 4096개의 행들로 이루어진 장방형 구조

- 각 기억 장소에는 4개의 데이터 비트들을 저장

기억 장소의 수 = 16M 개

- 전체 24비트의 주소 선들이 필요

※ RAS(Row Address Strobe) 신호와 CAS(Column Address Strobe)신호를 이용하여, 칩으로 실제 입력되는 주소 비트(선)의 수는 12개만 되도록 함

기억장치 제어기 (memory controller) :

CPU가 생성한 주소를 행 주소와 열 주소로 나누어 순차적으로 DRAM으로 전송하고, 그에 맞추어 RAS 및 CAS 신호를 발생시키는 하드웨어 모듈

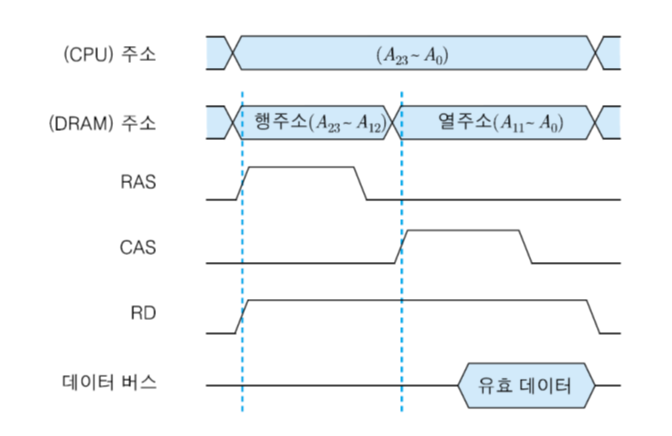

RAS (Row Address Strobe) 신호 : 행 주소를 가리키는 제어 신호

CAS (Column Address Strobe) 신호 : 열 주소를 가리키는 제어 신호

DRAM 읽기 동작의 타이밍도

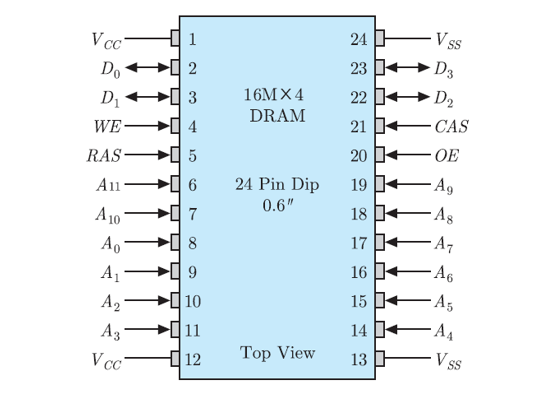

64M(16Mx4) bit DRAM 패키지의 입출력 핀 구성

Vcc : 전원 공급 핀

Vss : 접지 핀

D0~D3 : 데이터 입출력 핀

A0~A11 : 주소 핀

WE : 쓰기 신호 선

OE : 읽기 신호 선

RAS : RAS 신호 선

CAS : CAS 신호 선

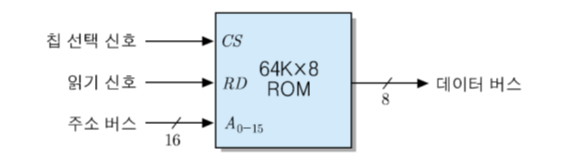

5.3.2 ROM (Read Only Memory)

- 영구 저장이 가능한 반도체 기억장치

- 읽는 것만 가능하고, 쓰는 것은 불가능 (RD신호만 있으면 된고, 데이터 버스가 단방향)

- 아래 내용들의 저장에 사용

> 시스템 초기화 및 진단 프로그램

> 빈번히 사용되는 함수들을 위한 서브루틴들

> 제어 유니트의 마이크로프로그램

ROM의 종류

- PROM(Programmable ROM) : 사용자가 한 번은 쓰는 것이 가능한 ROM

- EPROM(Erasable Programmable ROM) : 자외선을 이용하여 내용을 지우는 것이 가능한 PROM. 여러 번 쓰기가 가능

- EEPROM(Electrically Erasable PROM) : 전기적으로 지울 수 있는 EPROM. 데이터 갱신 횟수 제한 (수만 번 정도)

- 플래시 메모리(Flash memory) :

> NAND형 : 페이지(2KB/4KB) 단위 읽기/쓰기 가능, 블록(64/128페이지) 단위 삭제, [NOR형은 바이트 단위 읽기/쓰기 가능]

> EEPROM에 비하여 삭제 시간이 더 빠르고, 집적 밀도도 더 높음

> 삭제 횟수 제한 (100,000 ~ 1,000,000회)

> 하드 디스크를 대체하는 SSD(solid-state-drive)의 구성요소

'Computer Science > Computer Architecture' 카테고리의 다른 글

| 05. 기억장치 (5) [캐시 메모리] (0) | 2020.05.08 |

|---|---|

| 05. 기억장치 (4) [기억장치 모듈의 설계] (0) | 2020.04.30 |

| 05. 기억장치 (2) [계층적 기억장치시스템] (0) | 2020.04.30 |

| 05. 기억장치 (1) [기억장치의 분류와 특성] (0) | 2020.04.30 |

| 04. 제어 유니트 (4) [마이크로 프로그램의 순서제어] (0) | 2020.04.22 |

댓글 영역