고정 헤더 영역

상세 컨텐츠

본문

1. 기억장치 칩의 데이터 I/O 비트 수가 단어 길이보다 적은 경우

> 여러 개의 칩들을 병렬로 접속하여 기억장치 모듈을 구성

(단어의 길이 = N비트, 기억장치 칩의 데이터 I/O 비트 수 = B라면, -> N/B 개의 칩들을 병렬 접속)

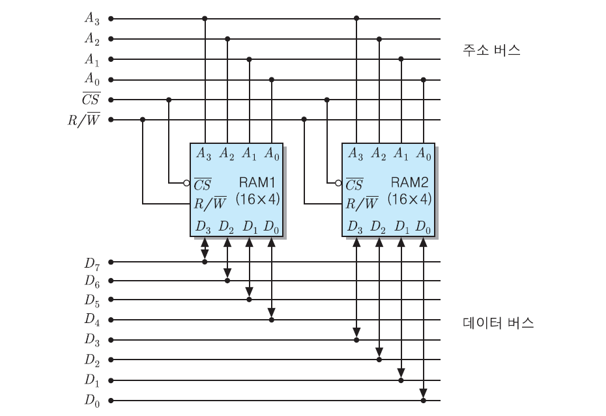

[EXAMPLE] N = 8 일때, 16x4비트 RAM 칩들을 이용한 기억장치 모듈의 설계

- 방법 : 2개의 RAM 칩들을 병렬로 접속

- 모듈의 용량 : (16x4) x 2개 = 16x8비트 = 16바이트

- 주소 비트 (4개 : A3~A0) : 두 칩들에 공통으로 접속

- 칩 선택 (Chip Select : CS)신호도 두 칩들에 공통으로 접속

- 주소 영역 : 0000 ~ 1111

16x4 비트 RAM 칩들을 이용한 16x8비트 기억장치 모듈

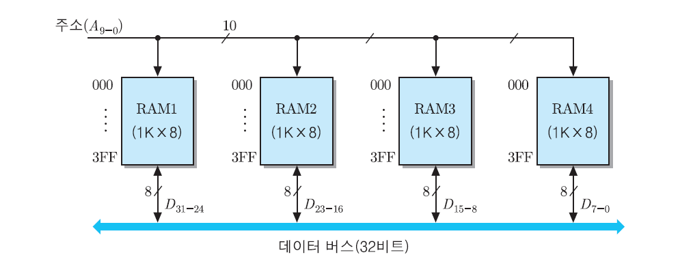

[EXAMPLE] 1K x 8비트 RAM 칩들을 이용한 1K x 32비트 기억장치 모듈의 설계

- 방법 : 4개의 RAM 칩들을 병렬 접속

- 모듈의 용량 : (1Kx8) x 4개 = 1K x 32비트 = 1Kword

- 주소 비트 (10개 : A9~A0) : 모든 칩들에 공통으로 접속

- 주소 영역 : 000H ~ 3FFH (단, H는 16진수 표시)

- 데이터 저장 : 동일한 기억장치 주소에 대하여 칩 당 (32비트들 중의) 8비트 씩 분산 저장

1K x 32 비트 기억장치 모듈

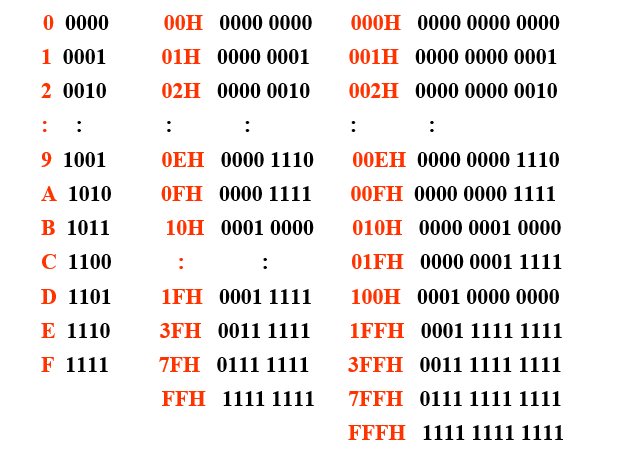

[참고] 16진수

2. 필요한 기억 장소의 수가 각 기억장치 칩의 기억 장소 수보다 많은 경우

> 여러 개의 칩들을 직렬 접속하여 기억장치 모듈을 구성

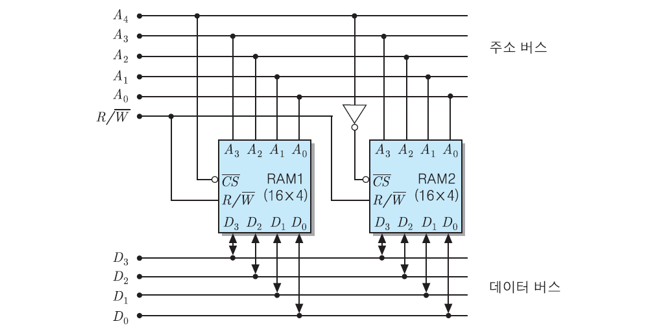

[EXAMPLE] 두 개의 16x4비트 칩들을 이용한 32x4비트 기억장치 모듈의 설계

- 방법 : 2개의 RAM 칩들을 직렬 접속

- 모듈의 용량 : 2개 x (16x4) = 32x4비트

- 주소 비트 수 : 5개 (A4~A0)

> A4 : 칩 선택 (CS) 신호로 사용

> A3~A0 : 두 칩들에 공통으로 접속

- 주소 영역

> RAM1 : 00000 ~ 01111

> RAM2 : 10000 ~ 11111

16x4비트 RAM 칩들을 이용한 32x4비트 기억장치 모듈

[EXAMPLE] 1Kx8비트 RAM 칩들을 이용한 4Kx8비트 기억장치 모듈

- 방법 : 4 개의 RAM 칩들을 직렬 접속

- 모듈의 용량 : (1Kx8) x 4개 = 4Kx8비트 = 4KByte

- 주소 비트 (12개 : A11 ~ A0) 접속 방법

> 상위 2 비트 (A11, A10) : 주소 해독기를 이용하여 네 개의 칩 선택(CS) 신호 발생

> 하위 10 비트 (A9~A0) : 모든 칩들에 공통으로 접속

- 전체 주소 영역 : 000H ~ FFFH

- 데이터 버스 : 모든 기억장치 칩에서 공통 접속

> 한 번에 8비트씩 엑세스

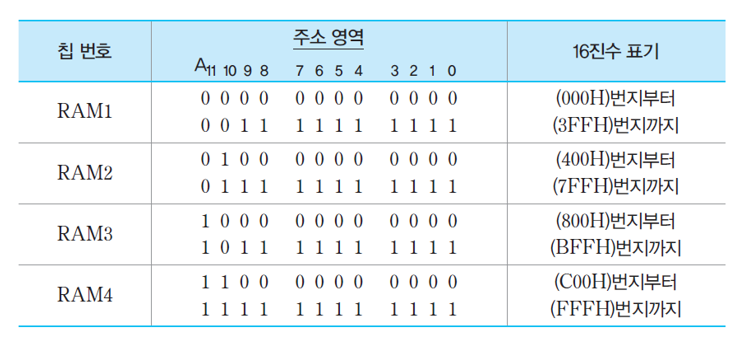

- 각 RAM에 지정되는 주소 영역

4K x 8비트 기억장치 모듈

기억장치 모듈의 설계 순서

1. 컴퓨터시스템에 필요한 기억장치 용량 결정

2. 사용할 칩들을 결정하고, 주소 표(address table; address map이라고도 함)를 작성

3. 세부 회로 설계

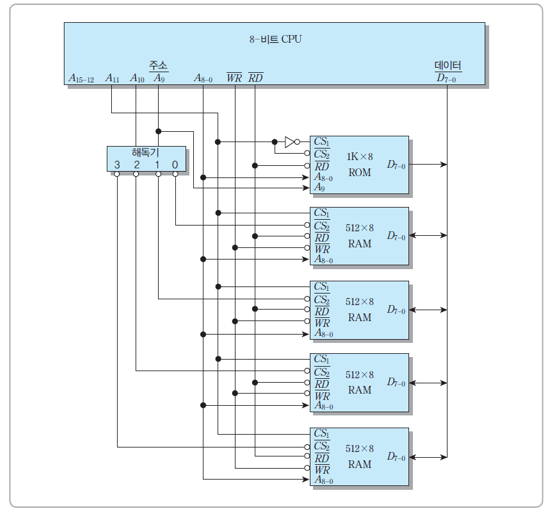

[EXAMPLE] 8-비트 마이크로컴퓨터를 위한 기억장치의 설계

• 필요 용량 : 1KByte ROM, 2KByte RAM

• 주소 영역 : ROM = 0번지부터, RAM = 800H 번지부터

• 사용 가능한 칩들 : 1K×8bit ROM, 512×8bit RAMs

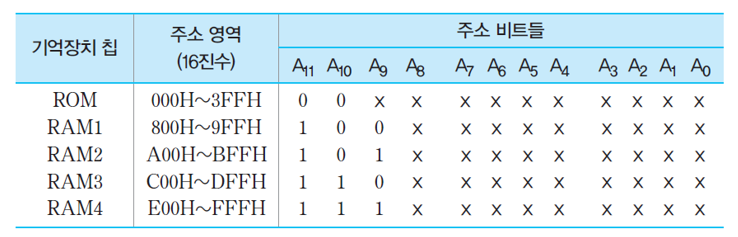

기억장치 주소 표 (memory address map)

- A11비트로 0일땐 ROM, 1일땐 RAM 구분, A10, A9 비트로 RAM1부터 RAM4까지 구분

세부 회로 설계

'Computer Science > Computer Architecture' 카테고리의 다른 글

| 05. 기억장치 (5) [캐시 메모리 - 사상방식] (0) | 2020.05.08 |

|---|---|

| 05. 기억장치 (5) [캐시 메모리] (0) | 2020.05.08 |

| 05. 기억장치 (3) [반도체 기억장치] (0) | 2020.04.30 |

| 05. 기억장치 (2) [계층적 기억장치시스템] (0) | 2020.04.30 |

| 05. 기억장치 (1) [기억장치의 분류와 특성] (0) | 2020.04.30 |

댓글 영역