고정 헤더 영역

상세 컨텐츠

본문

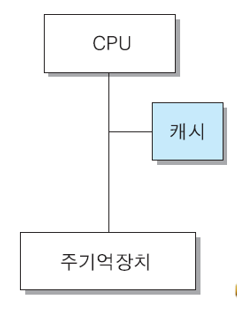

캐시 메모리 (Cache memory)

- CPU와 주기억장치의 속도 차이로 인한 CPU 대기 시간을 최소화 시키기 위하여, CPU와 주기억장치 사이에 설치하는 고속 반도체 기억장치

특징

- 주기억장치(DRAM)보다 엑세스 속도가 더 높은 칩(SRAM)사용

- 가격 및 제한된 공간 때문에 용량이 적다

- 캐시 적중(cache hit) : CPU가 원하는 데이터가 캐시에 있는 상태

- 캐시 미스(cache miss) : CPU가 원하는 데이터가 캐시에 없는 상태 (주기억장치로부터 데이터를 읽음)

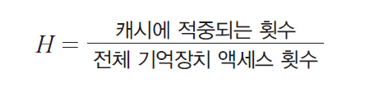

- 적중률(hit ratio) : 캐시에 적중되는 정도(H)

- 캐시의 미스율(miss ratio) = (1-H)

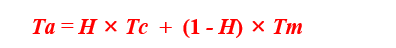

- 평균 기억장치 엑세스 시간(Ta) (Tc는 캐시 엑세스 시간, Tm은 주기억장치 엑세스 시간)

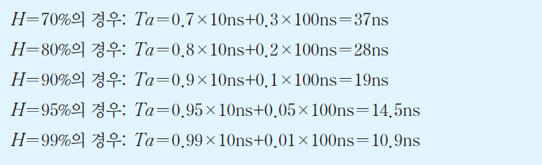

캐시 적중률과 평균 기억장치 엑세스 시간의 관계

- Tc = 10ns, Tm = 100ns 인 경우

- 캐시의 적중률이 높아질수록 평균 기억장치 엑세스시간은 캐시 엑세스 시간에 접근

- 캐시 적중률은 프로그램과 데이터의 지역성(locality)에 따라 달라짐

지역성(locality)

- 시간적 지역성(temporal locality) : 최근에 엑세스된 프로그램이나 데이터가 가까운 미래에 다시 엑세스 될 가능성이 높다.

- 공간적 지역성(spatial locality) : 기억장치내에 인접하여 저장되어 있는 데이터들이 연속적으로 엑세스 될 가능성이 높다.

- 순차적 지역성(sequential locality) : 분기(branch)가 발생하지 않는 한, 명령어들은 기억장치에 지정된 순서대로 인출되어 실행된다.

캐시 설계에 있어서의 공통적인 목표

- 캐시 적중률의 극대화

- 캐시 엑세스 시간의 최소화

- 캐시 미스에 따른 지연 시간의 최소화

- 주기억장치와 캐시 간의 데이터 일관성 유지 및 그에 따른 오버헤드의 최소화

5.1 캐시의 크기(용량)

- 용량이 커질수록 적중률이 높아지지만, 비용이 증가

- 용량이 커질수록 주소 해독 및 정보 인출을 위한 주변 회로가 더 복잡해지기 때문에 엑세스 시간이 다소 더 길어짐

5.2 인출 방식

- 요구 인출(demand fetch) 방식 : 필요한 정보만 인출해 오는 방법

- 선인출(prefetch) 방식 : 필요한 정보 외에 앞으로 필요할 것으로 예측되는 정보도 미리 인출, 지역성이 높은 경우에 좋음

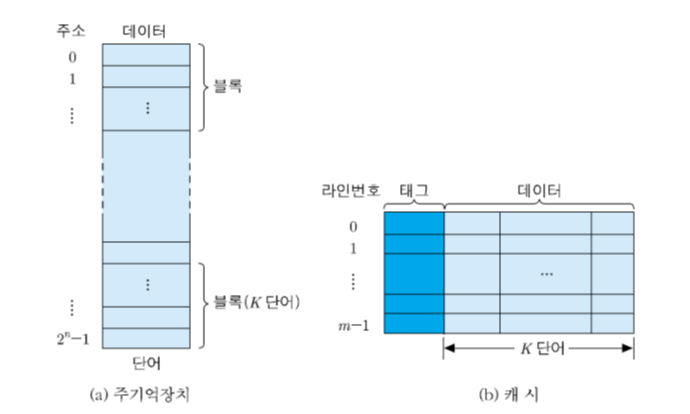

주기억장치와 캐시의 조직

- 주기억장치 블록 (K개의 단어들로 구성) : 하나의 캐시 라인(cache line)에 적재

- 블록(block) : 주기억장치로부터 동시에 인출되는 정보들의 그룹

> 주기억장치 용량 = 2^n 단어, 블록 = K 단어 -> 블록의 수 = 2^n/K 개

- 라인(line) : 캐시에서 각 블록이 저장되는 장소

- 태그(tag) : 라인에 적재된 블록을 구분해주는 정보

'Computer Science > Computer Architecture' 카테고리의 다른 글

| 05. 기억장치 (5) [캐시 메모리 - 사상방식] (0) | 2020.05.08 |

|---|---|

| 05. 기억장치 (4) [기억장치 모듈의 설계] (0) | 2020.04.30 |

| 05. 기억장치 (3) [반도체 기억장치] (0) | 2020.04.30 |

| 05. 기억장치 (2) [계층적 기억장치시스템] (0) | 2020.04.30 |

| 05. 기억장치 (1) [기억장치의 분류와 특성] (0) | 2020.04.30 |

댓글 영역